니케이 일렉트로닉스 2025/12 저전력 AI 칩에 도전하는 프리퍼드, 절묘한 클럭 정지 모색

Nikkei Electronics요약

Nikkei Electorinics_25.12호

저전력 AI 칩에 도전하는 프리퍼드, 절묘한 클럭 정지 모색

설정 누락을 EDA로 추출, 차세대 MN-Core 개발에 적용

슈퍼컴퓨터의 에너지 효율성을 겨루는 Green500에서 3번이나 1위를 차지한 프리퍼드 네트웍스(Preferred Networks, 도쿄, 이하 PFN). 그 큰 원동력이 된 것은 자체 개발한 저전력으로 동작하는 AI(인공지능) 처리 칩 ‘MN-Core 시리즈’이다. 이 시리즈에는 다양한 저전력화 기술들이 도입되어 있다. ‘클럭 게이팅(Clock Gating)’도 그 중 하나이다. 이미 알려진 기술이지만, PFN만의 특별한 클럭 게이팅의 활용법을 PFN의 엔지니어가 클럭 게이팅 강연에서 설명했다.

-- 높은 전력 효율과 안정적인 동작을 목표로 --

PFN의 클럭 게이팅 강연은 지멘스 EDA 재팬의 프라이빗 이벤트 ‘Siemens EDA Tech Forum 2025 Japan’(2025년 9월 5일, 도쿄 개최)에서 진행되었다. 발표한 사람은 PFN의 다카쓰카(高務) 엔지니어. 강연 제목은 ‘‘PowerPro Designer’를 이용한 AI 가속기(AI Accelerator)의 높은 전력 효율과 안정적 동작의 양립을 목표로 한 설계’였다.

다카쓰카 엔지니어에 따르면, PFN은 AI 학습 및 HPC(High Performance Computing)용으로 MN-Core 시리즈를 개발해왔다. 시중에 판매되는 GPU(그래픽처리장치) 칩(NVIDIA 제품)은 전력 소모가 크고, 공급량 부족 및 가격 상승으로 인해 쉽게 구입하기 어렵다는 것이 그 배경에 있다.

-- 전력 효율을 소프트웨어로 제어 --

앞서 언급한 바와 같이 MN-Core 시리즈의 가장 큰 특징은 저전력 동작이다. 다카쓰카 엔지니어에 따르면, MN-Core 시리즈는 범용 프로세서 IC(GPU와 MPU)와는 다른 칩 아키텍처를 채택, 이를 통해 높은 연산 성능과 전력 효율을 실현했다.

구체적으로는, 범용 프로세서에서 전용 회로로 처리되는 네트워크 제어와 캐시 제어, 명령 스케줄링을 MN-Core 시리즈에서는 소프트웨어가 담당한다(이하 MN-Core 소프트웨어 제어 기술). 즉, 컴파일 시에 이러한 제어를 확정할 수 있다.

이를 통해 연산기와 레지스터가 차지하는 칩 면적이 늘어나 연산 성능이 향상된다. 더 나아가 소프트웨어를 갱신하는 것만으로 내부 회로의 제어 절차를 바꿀 수 있어 저전력화(즉, 높은 전력효율화)가 용이하다고 한다.

-- 클럭 정지를 세밀하게 제어 --

MN-Core 시리즈에는 MN-Core 소프트웨어 제어 기술과 함께 범용 프로세서 IC와 마찬가지로 회로 레벨에서도 저전력화 기술이 도입되어 있다. 즉, 사용되지 않는 회로의 동작을 정지시키는 것이다. 회로의 동작을 정지시키는 방법에는 여러 가지가 있으며, 클럭 게이팅도 그 중 하나이다.

클럭 게이팅이란 회로에 대한 클럭 공급을 멈춤으로써 그 회로의 동작을 정지시키는 기술이다. MN-Core 소프트웨어 제어 기술을 통해 범용 프로세서 IC에 비해 세밀한 레벨에서 클럭 게이팅이 이루어진다.

MN-Core 시리즈의 설계에서 클럭 게이팅 설정은 RTL(Register Transfer Level)에 있어서 사람이 실시해왔다. 아마도 이 점 때문에 PFN이 Green500에서 1위를 차지했을 당시 사용된 MN-Core 칩에서 클럭 게이팅 설정이 누락되는 문제가 발생한 것으로 보인다. 다른 방법을 강구해 이를 보완했기 때문에 Green500에서 1위를 차지할 수 있었지만, 클럭 게이팅 설정 누락을 없애기 위해 EDA(Electronic Design Automation) 툴 도입을 검토하게 되었다고 한다.

-- 자동 처리되지 않는 툴을 선택 --

PFN이 클럭 게이팅 설정 누락을 방지하기 위한 EDA 툴로 검토한 제품은 미국 Siemens EDA의 ‘PowerPro Designer’와 ‘PowerPro Optimizer’이다.

PowerPro Designer는 RTL의 회로 정보를 입력하면 클럭 게이팅 후보를 제안한다. 또한, 소비전력 등 회로 동작에 관련된 지표를 연산해 제시하는 기능도 있다. PowerPro Optimizer는 PowerPro Designer의 상위 버전으로, PowerPro Designer의 모든 기능에 더해 자동으로 클럭 게이팅을 설정할 수도 있다. 이 두 가지 모두 입력 벡터(논리회로를 작동시키는 입력 패턴)의 유무에 관계 없이 사용할 수 있다.

PFN이 선택한 것은 설계자가 직접 클럭 게이팅을 설정해야 하는 PowerPro Designer이다. PowerPro Optimizer가 설계 공수를 줄일 수 있지만, PowerPro Designer를 선택한 이유는 툴이 제안하는 클럭 게이팅 내용을 확인할 수 있다는 점과 MN-Core 시리즈는 회로 규모는 크지만 SIMD(Single Instruction Multiple Data) 방식의 프로세서이기 때문에 회로의 종류가 적어 사람이 처리하기에 적합하다고 판단했기 때문이다.

-- 클럭 게이팅의 부작용 --

클럭 게이팅을 실시하면 저전력화를 도모할 수 있지만, 부작용도 있다. 예를 들어, 클럭 게이팅하는 회로가 늘어나면 클럭 게이팅 전후로 전압이 크게 변화해 칩의 안정적 동작이 어려워진다. 실제로 다카쓰카 엔지니어는 “툴이 제안한 클럭 게이팅 후보 중 채택하지 않은 것이 있었다”라고 말했다.

이번 강연에서 그는 채택하지 않은 두 가지 사례를 소개했다. 첫 번째는 SRAM이나 레지스터 파일에 클럭 게이팅을 실시하는 경우이고, 두 번째는 피연산자(Operand)나 명령에 의존하는 클럭 게이팅이다.

예를 들어, 전자의 경우, 툴은 SRAM와 레지스터 파일 전단(Pre-stage)의 연산이 필요 없다고 판단해 연산기 전단의 SRAM와 레지스터 파일도 클럭 게이팅하도록 제안한다. 이것을 채택하면 연산기를 작동시킬 수 없게 된다. “논리적 기능 측면에서는 맞지만, 소비전력을 평준화하기 위해 연산기를 작동해야 하는 경우가 있어 그것이 불가능해지는 것은 바람직하지 않다고 판단했다”(다카쓰카 엔지니어).

-- 마지막은 사람이 검증 --

현재 PFN은 PowerPro Designer를 사용해 차세대 MN-Core와 추론 전용 칩 개발을 추진하고 있다. 앞에서 언급했듯이, EDA 툴은 클럭 게이팅 후보를 제시할 뿐만 아니라, 다수의 후보 중에서 우선순위가 높은 것을 찾는 데 도움을 준다. 이로 인해 클럭 게이팅 설정의 작업 효율이 높아진다. 구체적으로는, 툴이 제시하는 회로 동작에 관련된 지표를 참조해 우선적으로 처리할 클럭 게이팅 후보를 찾아낼 수 있다. 툴이 제시하는 지표는 여러 가지가 있지만, 다카쓰카 엔지니어가 추천하는 지표는 ‘Weighted Frequency(주파수×비트폭)’이다. 소비전력도 제시되지만, RTL 단계에서 추정한 소비전력은 실제 칩의 소비전력과 차이가 나는 경우가 있다. 이것보다는 클럭 게이팅으로 줄어드는 다이나믹 전력과 관련이 깊은 주파수에 주목하는 것이 현실적이라고 한다.

-- 효과와 부작용 산출을 목표로 --

PowerPro Designer 도입 효과가 나타나면서 칩 개발 부문 내에서 클럭 게이팅에 대한 인식이 높아졌다고 한다. PFN은 앞으로 클럭 게이팅을 더욱 효과적으로 활용할 수 있도록 클럭 게이팅의 효과인 전력 절감 양과 부작용인 전력 변동을 쉽게 파악할 수 있는 방법을 개발할 방침이다. 예를 들어, 논리 시뮬레이션 결과를 참조해 효과와 부작용을 산출하는 연산식의 정의 등이 있다.

-- 끝 --

Copyright © 2025 [Nikkei Electronics] / Nikkei Business Publications, Inc. All rights reserved.

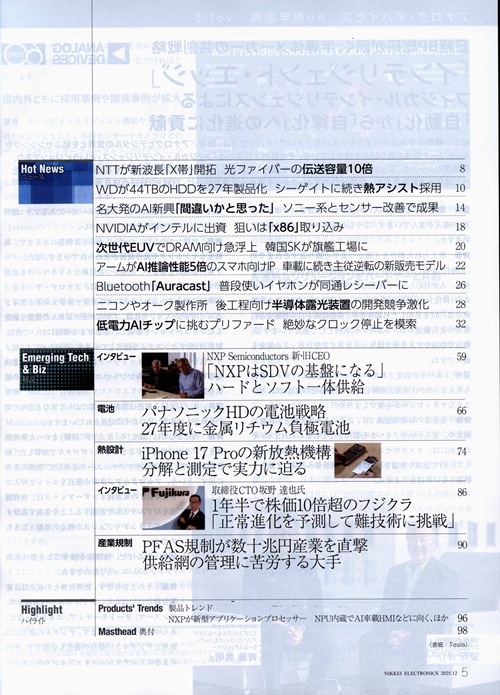

목차

목차_Nikkei Electronics_2025.12

Hot News

NTT가 새로운 파장 ‘X대’ 개척, 광섬유의 전송 용량 10배 증가

-- 광 증폭기와 송수신기의 신규 개발 없이도 실현 가능

WD가 44TB HDD를 2027년에 제품화, Seagate에 이어 열 어시스트 채택

-- 일본에서의 연구개발 강화, 니어라인 스토리지 수요에 대응

“결과를 믿을 수 없었다”, 나고야대학 발 AI 스타트업이 소니 계열사와 센서 개선에서 성과

-- 아이크리스탈의 고이시 대표이사

NVIDIA가 인텔에 출자, ‘x86’ 도입 노려

-- NVLink로 GPU와 CPU를 고속 통신, AMD에는 역풍

차세대 EUV에서 DRAM용 급부상, 한국 SK가 플래그십 공장에 도입

-- HBM으로 도약한 DRAM 사업의 우위 유지를 목표로

Arm이 AI 추론 성능을 5배 높인 스마트폰용 IP 발표, 차량용에 이어 주종 관계 역전의 새로운 판매 모델

-- IP 코어셋 도입으로 SoC 벤더의 부담 줄어

Bluetooth ‘Auracast’, 일상용 이어폰이 동시통역 수신기로

-- 음성을 수십 미터 범위에 브로드캐스트, 작은 라디오국으로 기능

후공정용 반도체 노광장치 개발 경쟁 격화, 니콘과 오크제작소도 고해상도 제품 출시

-- 패널 레벨 패키지에서 마스크리스 수요 확대, AI 시장에서 격돌

저전력 AI 칩에 도전하는 프리퍼드, 절묘한 클럭 정지 모색

-- 설정 누락을 EDA 툴로 추출, 차세대 MN-Core 개발에 적용

Breakthrough 특집 1

주력 전원 ‘축전 발전소’

제1부 : 세계 동향

전 세계적으로 축전 발전소 증가, 이미 미국 캘리포니아에서는 주요 전원으로

제2부 : 축전 시스템

멈추지 않는 가격 하락, 테슬라는 전기차 수준의 생산 규모를 목표로

제3부 : 국내 동향

국내 축전 발전소의 투자액이 1조 엔 넘어, 300GWh 시장은 이미 포화 상태인가?

Emerging Tech&Biz

인터뷰

“NXP는 SDV의 기반이 된다”, 하드웨어와 소프트웨어 일체를 공급

NXP Semiconductors의 신∙구 CEO

배터리

파나소닉홀딩스의 배터리 전략, 2027년에 금속 리튬 음극 배터리

열 설계

iPhone 17 Pro의 새로운 방열 메커니즘, 분해와 측정으로 성능 확인

인터뷰

1년 반 만에 주가가 10배 이상 상승한 후지쿠라, “정상적인 진화를 예측해 난이도 높은 기술에 도전”

후지쿠라의 사카노 이사 겸 CTO

산업 규제

PFAS 규제가 수십조 엔 규모의 산업 직격, 공급망 관리에 어려움을 겪는 대기업들

Products' Trends

NXP, NPU가 내장된 애플리케이션 프로세서 발표, 로컬 디밍 가능

-- 끝 --

Copyright © 2025 [Nikkei Electronics] / Nikkei Business Publications, Inc. All rights reserved.