일경일렉트로닉스_2023/11(3)_반도체 AI설계 지원의 위력, 설계공수 1/30로,

Nikkei Electronics

- 목차

-

Hot News

▣ 라피더스 기공식에 관련 대기업이 총출동, 반도체 무리 형성에 착착 전진

-- 니시무라(西村) 경제산업 장관 회견, 기시다(岸田) 수상도 메시지

▣・iPhone 15시리즈 출시, 소문대로 USB-C나 잠망경 렌즈 탑재

-- 프리즘에서의 4회 반사로 최대 5배 줌으로

▣ JAXA가 도전하는 세계 최초 ‘달 표면 정밀 착륙’ 오차 100m 이내 -- 착륙 성공이면 인도에 이어 세계에서 다섯 번째

▣ 인텔이 24년 출하하는 신세대 Xeon, AMD에 5년 늦게 칩렛(Chiplet) 기반으로

요약

Nikkei Electronics_2023.11 Hot News (p26~30)

반도체 AI설계 지원의 위력

설계 공수 1/30로 줄어, 소니세미컨덕터솔루션즈와 캐논이 검증

반도체 IC(집적회로) 개발에 AI(인공지능)/기계학습 기술을 적용하여 설계 비용 및 기간을 줄이거나, IC를 고도화시키는 사례가 늘고 있다. 처리해야 할 데이터량이 증가해 IC가 대규모·복잡화되고 있는 한편, IC 설계 기간 단축 및 소비전력 절감이 요구되고 있기 때문이다.

이러한 상황을 배경으로 IC 설계에서 사용되는 EDA(Electronic Design Automation) 소프트웨어(이하 EDA 툴)에 기계학습 기술이 도입되고 있다. 이미지 센서의 신호 처리 IC를 사용해 기계학습 기술이 적용된 EDA 툴의 성능을 평가한 결과를 소니세미컨덕터솔루션즈와 캐논이 각각 ‘Cadence LIVE Japan 2023’(2023년 7월 14일, 요코하마 시)에서 발표했다.

IC설계에서는 성능(처리속도)과 소비전력, 칩 면적과 같은 복수의 요구 사양을 충족시키는 것이 요구된다. 하지만 요구 사양간에 서로 맞지 않는 케이스도 적지 않다. 예를 들면, 고성능(고속)의 IC는 소비 전력과 칩 면적이 커져 버린다. 한편, 칩 면적을 작게 하면 성능이 낮아질 수 있다. 이 때문에 EDA 툴을 사용할 때에는 어떤 요구를 우선시할 것인가를 파라미터로 지정할 필요가 있다.

하지만 파라미터의 설정을 잘못하면, 원하는 사양의 설계 결과를 얻을 수 없게 된다. 이럴 경우, 파라미터를 다시 설정하고 EDA 툴을 재가동해야 한다. 경험이 적은 설계자는 몇 번이나 파라미터를 다시 설정하는 경우가 많아 설계 기간의 장기화로 이어질 수 있다.

이 때문에 EDA 툴 벤더들은 기계학습 기술을 사용해 파라미터 설정을 최적화하는 시도를 5년 정도 전부터 본격화하고 있다. 예를 들어, 국내에서는 르네사스일렉트로닉스 등 대규모 IC를 설계하는 반도체 업체들이 이용하기 시작하는 등, 기계학습 기술을 적용한 EDA 툴을 이용하는 저변이 점차 확대되고 있다.

미국 Cadence Design Systems의 EDA 툴 유저 모임인 ‘Cadence LIVE Japan 2023’에서는 소니세미컨덕터솔루션즈와 캐논이 Cadence의 ‘Cadence Cerebrus Intelligent Chip Explorer’(이하, Cerebrus)라고 부르는 기계학습 기술을 응용한 제품을 평가한 결과에 대해 강연했다.

Cerebrus는 IC의 Register Transfer Level(RTL) 논리에서 마스크 레벨 레이아웃(Mask level layout)까지의 설계, 이른바 임플리멘테이션(Implementation) 설계를 기계학습 기술로 효율화한다.

소니 세미컨덕터솔루션즈와 캐논도 이미지 센서의 신호처리 IC에 포함되는 로직회로 설계에 Cerebrus를 적용해 그 실력을 평가하였다. 양 사 모두 숙련된 설계자가 매개변수를 설정했을 때보다 IC의 소비전력이 줄었고, 설계 기간도 크게 단축되었다고 보고했다.

-- 파라미터를 조정해 최적화 --

이번에 평가 대상이 된 Cadence의 Cerebrus는 Cadence가 만든 여러 EDA 툴의 파라미터를 자동으로 최적화할 수 있다. 파라미터의 설정에 사용하는 초기의 기계 학습 모델(추론용의 학습이 끝난 모델)은 Cadence가 마련해놓고 있다.

Cerebrus는 파라미터를 조정하면서 대상 EDA 툴을 가동시키고, 그 결과를 통해서 기계학습 모델을 개선해 원하는 사양으로 설계를 최적화해 나간다. 학습이 끝난 모델은 파생설계에도 적용할 수 있다.

소니세미컨덕터솔루션즈는 논리합성툴 ‘Genus Synthesis Solution’(이하 Genus)과 자동배치 배선툴 ‘Innovus Implementation System’(이하 Innovus)에 Cerebrus를 적용한 결과를 보고했다. 논리 합성 툴은 임플리멘테이션 설계의 전(前)단계를 처리. 즉, RTL 설계 데이터를 게이트 레벨 넷리스트(Gate level netlist)로 변환한다.

자동 배치 배선 툴은 임플리멘테이션 설계의 후(後)단계를 처리한다. 즉, 게이트 레벨 넷리스트를 마스크 레벨 레이아웃으로 자동 변환하는 것이다. 캐논은 Innovus에 Cerebrus를 적용한 결과와 Cerebrus에 포함되어 있는 플로어플랜 기능을 평가한 결과를 보고했다.

-- 600만 게이트 규모의 회로로 검증 --

이번 유저 모임에서 강연한 소니세미컨덕터솔루션즈의 혼다(本田) 씨(디자인&시스템 기술 플랫폼 부문 설계 기술 개발부 1과)에 따르면, 이미지 센서의 신호 처리 IC는 코스트 저감 요구가 강해 첨단이 아닌 레거시 프로세스를 사용하거나, 칩 상의 배선 층수를 4~5층으로 낮추고 있다고 한다.

소니세미컨덕터솔루션즈는 이러한 신호처리 IC의 특징을 감안해 40nm 프로세스로 제조하는 600만 게이트 규모의 로직 회로를 사용해 Cerebrus를 평가했다.

같은 회로를 대상으로 2종류의 평가를 실시했다. 즉, (1)자동배치배선 툴 Innovus에 Cerebrus를 적용한 평가 (2) Innovus와 논리합성 툴 Genus 에 Cerebrus를 적용한 평가이다. (1)의 평가에서는 숙련된 설계자가 파라미터를 설정한 가장 좋은 설계 결과와 비교해 소비전력 및 지연 시간이 개선된 것을 확인할 수 있었다.

구체적으로는 전체 소비전력은 2.86%, 누출전력은 4.67% 각각 줄었다. (2)의 평가에서는 소비전력이 더욱 개선된 것으로 나타났다. 전체 소비전력이 2.86%에서 6.36%로, 누출전력은 4.67%에서 9.72%로 개선 폭이 넓어졌다.

설계 기간과 설계 공수도 대폭 개선되었다. Innovus와 논리합성 툴 Genus에 Cerebrus를 적용해 파라미터를 최적화했을 경우, 숙련된 설계자에 의한 인력 최적화와 비교해 설계 기간은 3분의 1로, 설계 공수는 30분의 1로 대폭 절감할 수 있었다고 했다.

-- 소비전력 10% 이상 절감 --

캐논을 대표해 이번 유저 모임에서 강연한 사사키(佐木) 씨(가와사키(川崎)사업소 디바이스개발본부 반도체디바이스 제3설계부)는 이미지 센서의 신호 처리 IC 설계의 특징으로 로직 회로가 가늘고 긴 직사각형이라는 점을 들었다. 가늘고 긴 직사각형은 고유의 설계 제약이 있다고 했다. 또한, 저소비 전력화에 대한 요구가 매우 강하다는 점도 들었다.

사사키 씨는 2종류의 회로로 실시한 3가지 평가를 소개했다. 첫 번째 회로는 종횡비가 약 7로, 가늘고 긴 것. 약 250개의 하드 매크로를 포함하고 있으며, 이들이 점유하지 않은 칩 영역에는 500만 게이트 규모의 회로가 스탠다드 셀로 구성되어 있다. 이 설계에서는 Cerebrus를 사용함으로써 사람이 하는 설계에 비해 소비전력을 약 12.8% 절감, 설계 기간을 약 30% 단축할 수 있다는 것을 확인했다.

두 번째 회로는 26만 8,000게이트 규모로, 첫 번째보다 규모가 상당히 작지만 종횡비는 약 7.2로 거의 같다. 5개 층으로 배선하는 것도 같다. 규모가 작고 하드 매크로를 포함하지 않기 때문일 것이다. 첫 번째 회로보다 Cerebrus 적용의 효과는 작았다. 소비전력은 약 2.1% 절감, 설계 기간의 단축은 약 10%를 기록했다고 한다.

사사키 씨는 세 번째 사례로 첫 번째 회로의 하드 매크로 배치에 Cerebrus의 플로어플랜 기능 ‘Floorplan Explorer’를 적용한 결과에 대해 소개했다. Floorplan Explorer를 사용하지 않을 경우에는 사람이 하드 매크로를 배치해야 하지만, 이것을 사용하면 자동으로 배치할 수 있다.

사사키 씨는 “Floorplan Explorer를 사용하면 사람에 의한 하드 매크로 배치에 비해 소비전력을 약 3.3%, 설계 기간을 약 85% 줄일 수 있는 것으로 나타났다”라고 말했다.

-- 끝 --

Copyright © 2020 [Nikkei Electronics] / Nikkei Business Publications, Inc. All rights reserved.

목차

Hot News

▣ 라피더스 기공식에 관련 대기업이 총출동, 반도체 무리 형성에 착착 전진

-- 니시무라(西村) 경제산업 장관 회견, 기시다(岸田) 수상도 메시지

▣・iPhone 15시리즈 출시, 소문대로 USB-C나 잠망경 렌즈 탑재

-- 프리즘에서의 4회 반사로 최대 5배 줌으로

▣ JAXA가 도전하는 세계 최초 ‘달 표면 정밀 착륙’ 오차 100m 이내 -- 착륙 성공이면 인도에 이어 세계에서 다섯 번째

▣ 인텔이 24년 출하하는 신세대 Xeon, AMD에 5년 늦게 칩렛(Chiplet) 기반으로

-- 'Hot Chips 2023'에서 발표, 연산용과 I/O용 칩렛을 통합

▣ ACSL, '레벨4' 드론 개발 고투 총비용은 10억엔, 사원이 총출동하여 비행 시험

-- 국내 제1호기, 안전성 확보에 '리던던시성'과 '내장해성' 어프로치

▣ 반도체 AI 설계 지원 위력, ‘설계 공정수가 30분의 1로’

-- 소니 세미컨덕터 솔루션즈와 캐논이 검증

▣ 이종 칩 집적의 저비용화 목표, 다이렉트 노광을 유기 인터포저에

-- 오크제작소와 NEDO가 25년에 L/S=1.2μm 양산 시제기

▣ 스마트폰으로 천하를 잡은 Arm이 노리는 다음, 서버용 IP 코어 세트를 발표

-- 인텔과 AMD가 90% 억제하는 x86의 아성에 도전

▣ 한국 24년도는 탄력 예산, 배터리/반도체 등에 집중 투자

-- 연구개발 예산 총액은 감액, 중점분야는 6.3% 증가

▣ '기술자도 기업가도 크리에이터', CTO 오브 더 이어 수상자 강연

-- 대상에 소니 그룹 기타노(北野) 씨, 특별상에 NTT의 가와조에(川添) 씨와 미쓰비시케미컬 그룹의 Meixner 씨

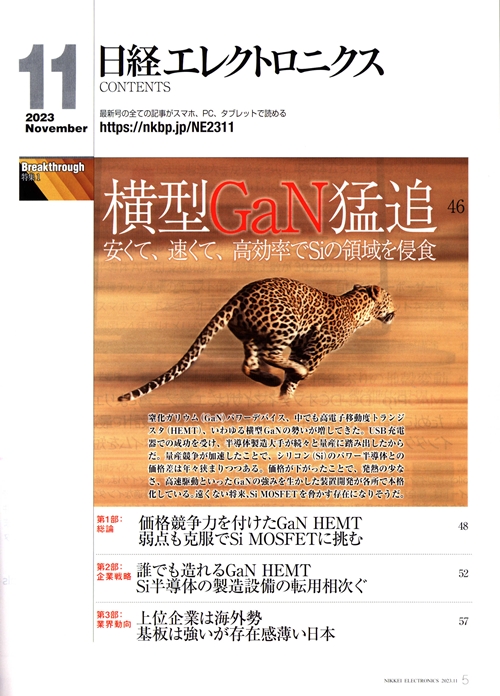

Breakthrough 특집 1

질화갈륨(GaN) 디바이스의 맹추격 -- 싸고,빠르고,고효율로 실리콘의 영역 침식

제1부: 총론

-- 가격 경쟁력을 갖춘 GaN HEMT, 약점도 극복해 Si MOSFET에 도전

제2부: 기업 전략

-- 누구나 만들 수 있는 GaN HEMT, 이어지는 Si 반도체 제조 설비의 전용

제3부 : 업계 동향

-- 상위는 해외 기업, 기판은 강하지만 존재감 약한 일본

Emerging Tech&Biz

반도체 -- 마이크로컴퓨터 시장에 15년만의 지각변동, 계기는 플래시 미세화 한계

디스플레이 -- 도레이가 범프까지 레이저 전사, 마이크로 LED 양산에 대한 벽 깨기

로보틱스 -- 지게차 운전자 부족으로 '무인기'에 각광, 노포/스타트업/중국업체 시장 쟁탈전

최고 기술자에게 묻다 -- '기술 로드맵은 만들지 않는다', 자원 배분으로 현장 컨트롤

닛케이 크로스테크 호평 기사 랭킹

2023년 9월의 닛케이 크로스테크 호평 기사 순위

New Products Digest

롬(Rohm)이 Si 커패시터에 참여, 30년에 3000억엔 시장에 도전하다 외